Integrated DSP+CPU architecture boosts efficiency processing in low power IoT devices

Stephen Law

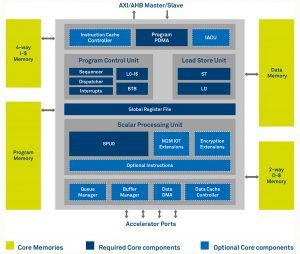

Electronics Semiconductors Engineering IoT Supply Chain CPU architecture CPU architecture IoT IoTCEVA-X1 IoT Processor implements a single-core DSP+CPU architecture, specifically designed to address the severe size, power and cost constraints imposed by the latest eMTC Cat-M1 and eNB-IoT Cat-NB2 standards, as well as future FeMTC and 5G cellular IoT deployments. The CEVA-Dragonfly NB1 pre-integrates the CEVA-X1 processor, an optimized RF, a baseband, and a protocol software to offer a complete Release 14 Cat-NB2 modem IP solution that reduces time-to-market and lowers entry barriers. The CEVA-X1 in the system can also serve as a multi-purpose, multi-mode processing hub for a range of tightly-associated IoT workloads, including Wi-Fi 802.11n, 802.11ac, Bluetooth/BLE, ZigBee/Thread, LoRa, SIGFOX, narrowband voice, GNSS and sensor fusion.